开导东说念主员可愚弄PIC16F13145系列单片机中的可建树逻辑模块(CLB)外设罢了硬件中复杂的分立逻辑功能,从而精简物料清单(BOM)并开导定制专用逻辑。

在很多镶嵌式系统应用中,经常王人会使用分立式逻辑器件,例如74'HC系列。这些逻辑器件的上风在于不错落寞于单片机(MCU)使命,况且反映速率比软件快得多。然而,这些器件会加多物料清单(BOM)况且需要占用迥殊的PCB面积。

为了料理这一问题,Microchip的很多单片机王人集成了一种名为可建树逻辑单位(CLC)的外设(在PIC® MCU上)或名为可建树定制逻辑(CCL)的类似外设(在AVR® MCU上)。这两种外设王人罢了了软件界说的定制逻辑,不错落寞于CPU试验。换句话说,一朝确立了定制逻辑功能,其行为就落寞于单片机。

然而,这两种外设存在赶走,即每个实例的逻辑数目相配小。每个CLC粗陋畸形于一个查找表(LUT),而CCL畸形于一个里面具有几个落寞LUT的实例。这两种外设的功能相配巨大,可用于开导浅显逻辑电路、将各式信号搀杂在一齐以及与其他硬件外设相集成。例如,硬件按钮去抖、WS2812输出身成和正交解码这些示例王人需要使用这两种外设,但单片机中这两种外设的数目并未几,因此赶走了应用的复杂度。

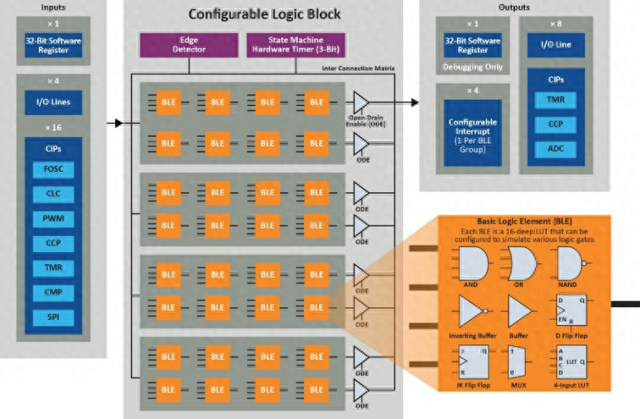

为了维持更复杂的应用,PIC16F13145系列单片机引入了一种名为可建树逻辑模块(CLB)的新式逻辑外设(如图1所示)。请留神,CLB并不会取代CLC或CCL外设,器件不错同期配备CLC/CCL和CLB。

图1—— CLB框图

PIC16F13145系列单片机上的CLB包含四个逻辑组,每组包含八个BLE。不同逻辑组的BLE之间彼此一语气——每个逻辑组代表两个GPIO输出和一个可选的CPU中断。当使命电压为5.5V时,BLE的传播时刻典型值小于6 ns。通盘结构中的通盘BLE共用一个天下时钟,那时钟源与可选的时钟分频器一齐在软件中进行建树。CLB不错使用单片机的里面时钟源之一或外部提供的时钟源。

该外设从单片机的存储器中进行开动化,之后可通过外设引脚继承(PPS)径直从自己结构中法例引脚。用户可通过PPS再行分拨用于硬件外设的I/O引脚,从而得到更大的狡计天真性。例如来说,要是SPI时钟先前使用RA1,但使用RA6会更故意,那么便不错通过PPS再行映射引脚。

CLB中的其他元件包括专用的3位硬件定时器(带解码输出)、用于输入信号的边沿检测器以及32位输出寄存器(用于调试)。单片机上的其他落寞于内核的外设(CIP)输出可用作CLB的输入,以便罢了更复杂的狡计。

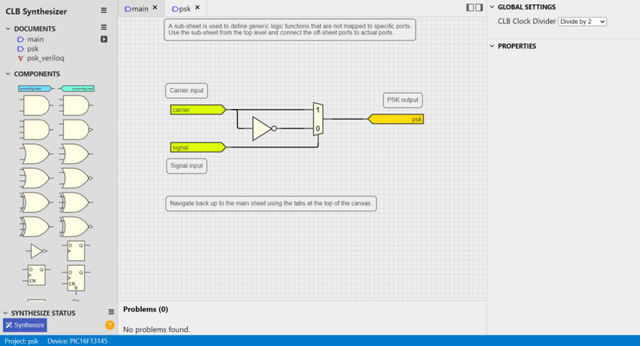

由于CLB比CLC或CCL复杂得多,因此Microchip开导了一款名为CLB合成器的新器具。CLB合成器提供了一个用于建树逻辑的图形界面,如底下的图2所示。除了逻辑原语除外,该器具还维持更高等的逻辑模块库(可由用户事前提供或定制)。

与该图形器具交互时,后台会自动生成一个Verilog模块用于合成。要是开导东说念主员更心爱编写我方的Verilog或者已准备好该文献,则不错将其动作模块径直导入器具。

图2——已洞开相移键控(PSK)示例的CLB合成器

CLB合成器的输出是一个汇编文献,其中包含用于确立CLB的比特流和一些用于将CLB建树为外设的源代码。该器具可通过MPLAB®代码建树器(MCC)或落寞在线器具运行。MCC是一款代码生成实用才略,允许用户使用可视化界面来确立和建树单片机中的外设。当硬件外设完成建树后,MCC将生成开动化代码和器件API。

在运行时,使用板上硬件径直从才略存储器加载CLB比特流。这种罢了的克己在于要是在才略运行时需要更动CLB建树,则不错使用存储在器件存储器中的不同比特流近似试验加载经由。

为了演示CLB的应用,咱们创建了一系列用例示例。这里咱们将商榷两个示例:7段暴露休养器和SPI至WS2812休养器。用例示例可动作构件复制以用作齐全料理决策的一部分。这里旨在展示该外设的实用性以及它大概为狡计带来哪些价值。

第一个用例是7段暴露休养器。7段暴露器可通过一组世俗的I/O引脚驱动,但步伐罢了经常需要使用软件界说的查找表将输入数字休养为稳健暴露器的正确输出样貌。在该罢了中,CLB充任硬件查找表。所需的输出字符(0到F)从软件加载到CLB输入寄存器中。暴露器的每个输出段均由LUT法例,以将输入映射到输出。

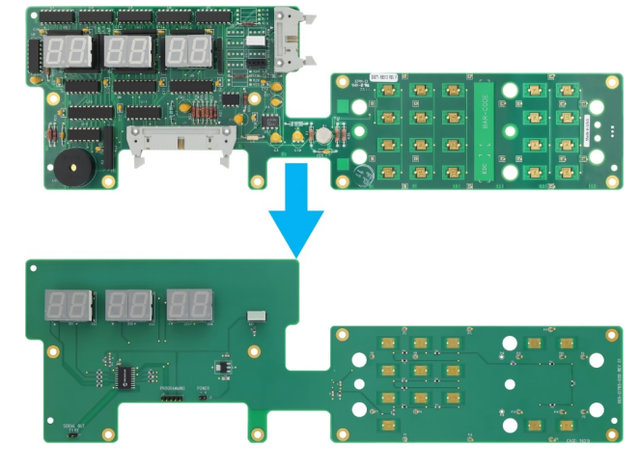

该用例示例在里面用于构建计时系统的新法例板。滥觞的用户界面是在20世纪80年代使用74'HC系列逻辑开导。使用CLB后,一个20引脚的单片机即可罢了电路板上的暴露和键盘逻辑,极地面精简了物料清单(BOM)。图3并列给出了两种决策以供比拟。

图3——原PCB与新PCB的并列比拟。该示例由Josh Booth开导。

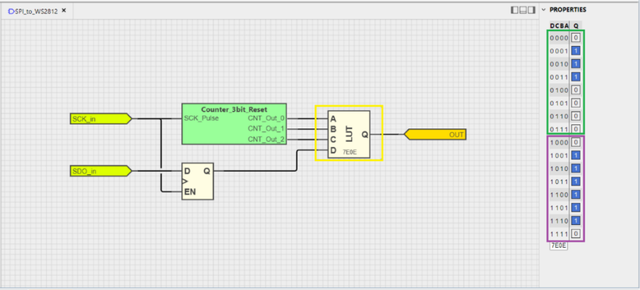

下一个示例是SPI至WS2812休养器。WS2812是一种单线串行条约,用于通过脉宽调制法例LED阵列。在本例中,SPI硬件用作要发送到LED的数据的移位寄存器,而CLB用于将SCLK和SDO休养为预期的输出。

在本例中,这是通过单触发3位计数器、带使能功能的D锁存器和4输入LUT来罢了,如底下的图4所示。该罢了的手艺体目下SPI和CLB的时钟源。SPI时钟确立为快活高电平、在高潮沿转换气象并以WS2812输出的频率(800 kHz)运行,而CLB的时钟源昔时者10倍的频率(8 MHz)运行。当SCLK为低电往常,将触发3位计数器并脱手计数。当计数到7(0b111)时,3位计数器将罢手并保合手为0,直到时钟脉冲的下一个低电平周期为止。

计数器的输出与输出数据的锁存版块一齐馈入4输入LUT。这将确立数据的输出样貌,如图4的右侧所示。计数器复位后,计数器输出将保合手为0以完成轮回。之后,可把柄需要发送SPI硬件中的下一个字节,近似该轮回。

图4——SPI至WS2812休养器框图(由Petre Teodor-Emilian开导)

这两个示例王人解释了单片机里面分立逻辑的上风。硬件外设可将CPU从各式任务中开脱出来,从而裁汰反映时刻并贬低功耗,同期减少元器件数目。有了CLB,之前无法在单片机里面罢了的复杂应用目下王人不错告成开导。目下,可赶赴Microchip直销网站或其他代理商处购买PIC16F13145系列单片机来获取CLB。开头: